# **SPU** Assembly Language Specification

Version 1.5

CBEA JSRE Series Cell Broadband Engine Architecture Joint Software Reference Environment Series

March 8, 2007

© Copyright International Business Machines Corporation, Sony Computer Entertainment Incorporated, Toshiba Corporation 2003, 2004, 2005, 2006, 2007

All Rights Reserved Printed in the United States of America March 2007

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

IBM PowerPC IBM Logo ibm.com

Cell Broadband Engine is a trademark of Sony Computer Entertainment, Inc.

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Systems and Technology Group 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351

The IBM home page can be found at **ibm.com**

The IBM semiconductor solutions home page can be found at ibm.com/chips

March 8, 2007

# **Table of Contents**

| List of Tables                                                 | iv     |

|----------------------------------------------------------------|--------|

| About This Document<br>Audience                                | v<br>v |

| Version History                                                | v      |

| Related Documentation                                          | vi     |

| Bit Notation and Typographic Conventions Used in This Document | vii    |

| 1. Introduction                                                | 1      |

| 2. Instruction Set and Instruction Syntax                      | 3      |

| 2.1. Notation and Conventions                                  | 3      |

| 2.2. Instruction Set                                           | 3      |

| 2.3. Aliases                                                   | 20     |

| 2.4. Channel Mnemonics                                         | 21     |

| 2.5. Immediate Values                                          | 22     |

| 2.6. Errors and Warnings                                       | 22     |

# **List of Tables**

| Table 2-1: Notations and Conventions        |

|---------------------------------------------|

| Table 2-2: SPU Assembler Instructions       |

| Table 2-3: Register and Instruction Aliases |

| Table 2-4: SPU Channels                     |

| Table 2-5: MFC Channels                     |

| Table 2-6: Valid Immediate Values           |

# **About This Document**

This document describes the Synergistic Processor Unit (SPU) assembly-language syntax for a processor compliant with the Cell Broadband Engine<sup>™</sup> Architecture (CBEA).

### Audience

The document is intended for system and application programmers who desire to write assembly language programs for the SPU.

# **Version History**

This section describes significant changes made to each version of this document.

| Version Number & Date      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v. 1.5<br>March 8, 2007    | Added several new double precision floating-point instructions (TWG_RFC00071-0).                                                                                                                                                                                                                                                                                                                                                                                        |

|                            | Corrected document version numbers for related documentation (TWG_RGC00093-0).                                                                                                                                                                                                                                                                                                                                                                                          |

| v. 1.4<br>October 11, 2006 | Changed several operands from rt to rc in the SPU Assembler<br>Instructions table (TWG_RFC00049-0: CORRECTION NOTICE), and<br>jsre-tool messages 00468 and 00488).                                                                                                                                                                                                                                                                                                      |

|                            | The description of the wrch instruction in the SPU Assembler Instructions table was corrected.                                                                                                                                                                                                                                                                                                                                                                          |

|                            | Applied changes made in TWG_RFC00061-1 and TWG_RFC00062-0.                                                                                                                                                                                                                                                                                                                                                                                                              |

| v. 1.3<br>October 20, 2005 | Changed "Broadband Processor Architecture" to "Cell Broadband<br>Engine Architecture", and changed "BPA" to "CBEA"<br>(TWG_RFC00037-0: CORRECTION NOTICE).                                                                                                                                                                                                                                                                                                              |

|                            | Deleted several references to BE revisions DD1.0 and DD2.0 (TWG_RFC00040-0: CORRECTION NOTICE).                                                                                                                                                                                                                                                                                                                                                                         |

| v. 1.2<br>July 13, 2005    | Deleted several sections in the "About This Document" chapter (TWG_RFC00032-0: CORRECTION NOTICE).                                                                                                                                                                                                                                                                                                                                                                      |

|                            | Corrected several documentation errors; for example, in several descriptions in the SPU Assembler Instructions table, the phrase "halfword element rt" was changed to "halfword element 1 of register rt" (TWG_RFC00033-0: CORRECTION NOTICE).                                                                                                                                                                                                                          |

| v. 1.1<br>June 10, 2005    | Changed "Broadband Engine" or "BE" to "a processor compliant with<br>the Broadband Processor Architecture" or "a processor compliant<br>with BPA"; and changed Synergistic Processing Unit to Synergistic<br>Processor Unit. Defined a PPU as a PowerPC Processor Unit on first<br>major instance. Corrected several book references and changed the<br>copyright page so that trademark owners were specified. (All changes<br>per TWG_RFC00031-0: CORRECTION NOTICE.) |

|                            | Made miscellaneous changes to the "About This Document" section.                                                                                                                                                                                                                                                                                                                                                                                                        |

| v. 0.9 - 1.0               | Not applicable. Version numbers were changed so that JSRE version<br>numbers are in synchrony with those used by IBM in its public<br>release.                                                                                                                                                                                                                                                                                                                          |

| Version Number & Date       | Changes                                                                                                                                                                         |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v. 0.8<br>May 12, 2005      | Changed PU to PPU; changed "PU-to-SPU" (mailboxes) and "SPU-<br>to-PU" to "inbound" and "outbound" respectively (TWG_RFC00028-1:<br>CORRECTION NOTICE).                         |

|                             | Updated channel names to coincide with BPA channel names (TWG_RFC00029-1).                                                                                                      |

| v. 0.7<br>July 16, 2004     | Removed all branch aliases from table of instruction aliases (TWG_RFC00009-0).                                                                                                  |

|                             | Added an additional SPU instruction, orx (TWG_RFC00010-0).                                                                                                                      |

|                             | Added mnemonics for channels that support reading the event mask and tag mask (TWG_RFC00011-0).                                                                                 |

|                             | Removed operands from hbrp instruction and provided a new description of this instruction. Also removed it from a table in section "2.6. Errors and Warnings" (TWG_RFC00012-0). |

|                             | Made miscellaneous editorial changes.                                                                                                                                           |

| v. 0.6<br>March 12, 2004    | Made miscellaneous editorial changes.                                                                                                                                           |

| v. 0.5<br>February 25, 2004 | Changed formatting of document so that it reflects the typographic conventions described on page vii. Made minimal editorial changes.                                           |

| v. 0.4<br>January 20, 2004  | Changed document to new format, including front matter. Made miscellaneous editorial changes.                                                                                   |

| v. 0.3                      | Corrected PC-relative addressing style.                                                                                                                                         |

| August 31, 2003             | Added low and high halfword address syntax.                                                                                                                                     |

|                             | Added stopd instruction.                                                                                                                                                        |

| v. 0.2                      | Added isolation control channel.                                                                                                                                                |

| May 13, 2003                | Replaced aci, asc, sbi, and ssb instructions with addx, cg, cgx, sfx, bg, and bgx.                                                                                              |

| v. 0.1<br>March 7, 2003     | Initial release of this document.                                                                                                                                               |

# **Related Documentation**

The following table provides a list of references and supporting materials for this document:

| Document Title                                                                                           | Version | Date              |

|----------------------------------------------------------------------------------------------------------|---------|-------------------|

| PowerPC User Instruction Set Architecture, Book I                                                        | 2.02    | January 28, 2005  |

| PowerPC Virtual Environment Architecture, Book II                                                        | 2.02    | January 28, 2005  |

| PowerPC Operating Environment Architecture, Book III                                                     | 2.02    | January 28, 2005  |

| PowerPC Microprocessor Family: The Programming<br>Environments for 32-Bit Microprocessors (G522-0290-01) | 1.0     | February 21, 2000 |

| Cell Broadband Engine Architecture                                                                       | 1.01    | October 2006      |

| Synergistic Processor Unit Instruction Set Architecture                                                  | 1.11    | October 2006      |

# Bit Notation and Typographic Conventions Used in This Document

#### **Bit Notation**

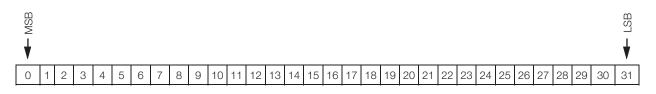

Standard bit notation is used throughout this document. Bits and bytes are numbered in ascending order from left to right. Thus, for a 4-byte word, bit 0 is the most significant bit and bit 31 is the least significant bit, as shown in the following figure:

#### MSB = Most significant bit

LSB = Least significant bit

Notation for bit encoding is as follows:

- Hexadecimal values are preceded by 0x. For example: 0x0A00.

- Binary values in sentences appear in single quotation marks. For example: '1010'.

#### **Other Typographic Conventions**

In addition to bit notation, the following typographic conventions are used throughout this document:

| Convention                | Meaning                                                                                                                                                                                                                                                                           |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| courier                   | Indicates programming code, processing instructions, register names,<br>data types, events, file names, and other literals. Also indicates function<br>and macro names. This convention is only used where it facilitates<br>comprehension, especially in narrative descriptions. |

| courier +<br>italics      | Indicates arguments, parameters and variables, including variables of type const. This convention is only used where it facilitates comprehension, especially in narrative descriptions.                                                                                          |

| italics (without courier) | Indicates emphasis. Except when hyperlinked, book references are in italics. When a term is first defined, it is often in italics.                                                                                                                                                |

| blue                      | Indicates a hyperlink (color printers or online only).                                                                                                                                                                                                                            |

viii About This Document

# **1. Introduction**

This specification describes SPU assembly-language syntax and machine-dependent features for the GNU assembler (as). Although this specification focuses on the GNU assembler, this document might also serve as an example specification for other SPU assemblers.

2 Introduction

# 2. Instruction Set and Instruction Syntax

# 2.1. Notation and Conventions

In this specification, lower case is used for all instructions, register aliases, and channels names; however, these tokens may also be expressed in upper or mixed case. Table 2-1 describes notations used in this specification.

| Table 2-1: | Notations a  | and C | conventions |

|------------|--------------|-------|-------------|

| 10010 2 1. | 1 totation o |       | 01100110110 |

| Notation/Convention | Meaning                                                                                                                                                                                                                |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ch                  | Channel number. Channels are specified as either \$ch followed by a channel number (for example, \$ch3) or a specific channel mnemonic. See section "2.4. Channel Mnemonics" for a complete list of channel mnemonics. |

| ra, rb, rc          | Source register. Registers are specified as a dollar symbol (\$) followed by a register number from 0 to127. For example, \$38 refers to register 38. See Table 2-3 for additional register aliases.                   |

| rt                  | Target register. Registers are specified as a dollar symbol (\$) followed by a register number from 0 to127. For example, \$38 refers to register 38. See Table 2-3 for additional register aliases.                   |

| s3, s6              | 3-bit or 6-bit signed value, respectively. Encoded as a 7-bit signed immediate in which only a subset of the bits is used.                                                                                             |

| s7                  | 7-bit sign-extended value.                                                                                                                                                                                             |

| s10                 | 10-bit sign-extended value.                                                                                                                                                                                            |

| s11                 | 11-bit sign-extended value.                                                                                                                                                                                            |

| s14                 | 14-bit sign-extended value.                                                                                                                                                                                            |

| s16                 | 16-bit sign-extended value.                                                                                                                                                                                            |

| s18                 | Relative address computations.                                                                                                                                                                                         |

| scale7              | 7-bit scale exponent. Values range from 0 to 127.                                                                                                                                                                      |

| spr                 | Special purpose register.                                                                                                                                                                                              |

| u3, u5, u6          | 3-bit, 5-bit, or 6-bit unsigned value, respectively. Encoded as a 7-bit unsigned immediate in which only a subset of the bits is used.                                                                                 |

| u7                  | Unsigned 7-bit value.                                                                                                                                                                                                  |

| u14                 | Unsigned 14-bit value.                                                                                                                                                                                                 |

| u16                 | Unsigned 16-bit value.                                                                                                                                                                                                 |

| u18                 | Unsigned 18-bit value.                                                                                                                                                                                                 |

### 2.2. Instruction Set

This section provides an overview of the SPU instruction set and its syntax, including:

- Supported instructions and their syntax

- Supported data types

- Supported ranges for instruction parameters

For details about the specific machine instructions, see the *Synergistic Processor Unit Instruction Set Architecture* specification.

#### Table 2-2: SPU Assembler Instructions

| Instruction/Usage | Description                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a rt, ra, rb      | Add word. Each word element of register $ra$ is added to the corresponding word element of register $rb$ , and the results are placed in the corresponding word elements of register $rt$ .                                                                                                                                                                                |

| absdb rt, ra, rb  | Absolute difference of bytes. Each byte element of register $ra$ is subtracted from the corresponding byte element of register $rb$ . The absolute values of the results are placed in the corresponding elements of register $rt$ .                                                                                                                                       |

| addx rt, ra, rb   | Add word extended. Each word element of register $ra$ , the corresponding word element of register $rb$ , and the least significant bit of the corresponding word element of register $rt$ are added, and the results are placed in the corresponding word elements of register $rt$ .                                                                                     |

| ah rt, ra, rb     | Add halfword. Each halfword element of register $ra$ is added to the corresponding halfword element of register $rb$ , and the results are placed in the corresponding halfword elements of register $rt$ .                                                                                                                                                                |

| ahi rt, ra, s10   | Add halfword immediate. The sign-extended immediate value $s10$ is added to each halfword element of register $ra$ , and the results are placed in the corresponding halfword elements of register $rt$ .                                                                                                                                                                  |

| ai rt, ra, s10    | Add word immediate. The sign-extended immediate value $s10$ is added to each word elements of register $ra$ , and the results are placed in the corresponding word elements of register $rt$ .                                                                                                                                                                             |

| and rt, ra, rb    | And. The value of register ra is logically ANDed with register rb, and the result is placed in register rt.                                                                                                                                                                                                                                                                |

| andbi rt, ra, s10 | And byte immediate. The 8 least significant bits of $s10$ are logically ANDed with each byte element of register $ra$ , and the results are placed in the corresponding elements of register $rt$ .                                                                                                                                                                        |

| andc rt, ra, rb   | And with complement. The value of register ra is logically ANDed with the complement of register rb, and the result is placed in register rt.                                                                                                                                                                                                                              |

| andhi rt, ra, s10 | And halfword immediate. The sign-extended immediate value $s10$ is logically ANDed with each halfword element of register $ra$ , and the results are placed in the corresponding elements of register $rt$ .                                                                                                                                                               |

| andi rt, ra, s10  | And word immediate. The sign-extended immediate value s10 is logically ANDed with each word element of register ra, and the results are placed in the corresponding elements of register rt.                                                                                                                                                                               |

| avgb rt, ra, rb   | Average bytes. The corresponding byte elements of registers ra and rb are averaged ((a+b+1) >> 1), and the results are placed in the corresponding byte elements of register rt.                                                                                                                                                                                           |

| bg rt, ra, rb     | Borrow generate word. Each unsigned word element of register ra is<br>compared to the corresponding unsigned word element of rb. If the value of<br>ra is greater than that of rb, a 0 is placed in the corresponding element of rt;<br>otherwise, a 1 is placed there.                                                                                                    |

| bgx rt, ra, rb    | Borrow generate word extended. Each word element of register ra is<br>subtracted from the corresponding word element of register rb. An additional<br>1 is subtracted from the result if the least significant bit of word element rt is<br>0. If the result is less than 0, a 0 is placed in the corresponding element of<br>register rt; otherwise, a 1 is placed there. |

| bi ra             | Branch indirect. Execution proceeds with the instruction at the address specified by word element 0 of register $ra$ . The 2 least significant bits of the address are ignored.                                                                                                                                                                                            |

| Instruction/Usage | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bid ra            | Branch indirect, disable. Execution proceeds with the instruction at the address specified by word element 0 of register $ra$ , and interrupts are disabled. The 2 least significant bits of this address are ignored.                                                                                                                                                                                                                                         |

| bie ra            | Branch indirect, enable. Execution proceeds with the instruction at the address specified by word element 0 of register $ra$ , and interrupts are enabled. The 2 least significant bits of the address are ignored.                                                                                                                                                                                                                                            |

| bihnz rc, ra      | Branch indirect if not zero halfword. If halfword element 1 of register $rc$ is 0, execution proceeds with the next sequential instruction; otherwise, execution proceeds at the address in word element 0 of register $ra$ . The 2 least significant bits of this address are ignored.                                                                                                                                                                        |

| bihnzd rc, ra     | Branch indirect if not zero halfword, disable. If halfword element 1 of register $rc$ is 0, execution proceeds with the next sequential instruction; otherwise, the branch is taken, and execution proceeds at the address in word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. If the branch is taken, interrupts are disabled; otherwise, the interrupt enable state remains unchanged.                            |

| bihnze rc, ra     | Branch indirect if not zero halfword, enable. If halfword element 1 of register $rc$ is 0, execution proceeds with the next sequential instruction; otherwise, the branch is taken, and execution proceeds at the address in word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. If the branch is taken, interrupts are enabled; otherwise, the interrupt enable state remains unchanged.                              |

| bihz rc, ra       | Branch indirect if zero halfword. If halfword element 1 of register $rc$ is 0,<br>execution proceeds at the address in word element 0 of register $ra$ . The 2<br>least significant bits of this address are ignored. Otherwise, the element $rc$ is<br>nonzero, and execution proceeds with the next sequential instruction.                                                                                                                                  |

| bihzd rc, ra      | Branch indirect if zero halfword, disable. If halfword element 1 of register $rc$ is 0, the branch is taken, and execution proceeds at the address in word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. Otherwise, execution proceeds with the next sequential instruction. If the branch is taken, interrupts are disabled; otherwise, the interrupt enable state remains unchanged.                                |

| bihze rc, ra      | Branch indirect if zero halfword, enable. If halfword element 1 of register $rc$ is 0, the branch is taken, and execution proceeds at the address in word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. Otherwise, the element $rc$ is nonzero, and execution proceeds with the next sequential instruction. If the branch is taken, interrupts are enabled; otherwise, the interrupt enable state remains unchanged. |

| binz rc, ra       | Branch indirect if not zero word. If word element 0 of register $rc$ is 0,<br>execution proceeds with the next sequential instruction; otherwise, execution<br>proceeds at the address in word element 0 of register $ra$ . The 2 least<br>significant bits of this address are ignored.                                                                                                                                                                       |

| binzd rc, ra      | Branch indirect if not zero word, disable. If word element 0 of register $rc$ is 0, execution proceeds with the next sequential instruction; otherwise, the branch is taken, and execution proceeds at the address in word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. If the branch is taken, interrupts are disabled; otherwise, the interrupt enable state remains unchanged.                                    |

| binze rc, ra      | Branch indirect if not zero word, enable. If word element 0 of register $rc$ is 0, execution proceeds with the next sequential instruction; otherwise, the branch is taken, and execution proceeds at the address in word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. If the branch is taken, interrupts are enabled; otherwise, the interrupt enable state remains unchanged.                                      |

| Instruction/Usage | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bisl rt, ra       | Branch indirect and set link. The effective address of the next instruction is taken from word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. The address of the instruction following this instruction is placed into word element 0 of register $rt$ , and all other word elements of $rt$ are assigned a value of zero.                                                                                                                                                                                                                                                                                       |

| bisld rt, ra      | Branch indirect and set link, disable. The effective address of the next instruction is taken from word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. The address of the instruction following this instruction is placed into word element 0 of register $rt$ , and all other word elements of $rt$ are assigned a value of zero. Interrupts are also disabled.                                                                                                                                                                                                                                                |

| bisle rt, ra      | Branch indirect and set link, enable. The effective address of the next instruction is taken from word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. The address of the instruction following this instruction is placed into word element 0 of register $rt$ , and all other word elements of $rt$ are assigned a value of zero. Interrupts are also enabled.                                                                                                                                                                                                                                                  |

| bisled rt, ra     | Branch indirect and set link on external data. The address of the instruction following this instruction is placed in word element 0 of register $rt$ , and all other elements of register $rt$ are assigned a value of zero. If the count of channel 0 is nonzero, execution continues at the effective address in word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. If the count of channel 0 is zero, execution continues with the next sequential instruction.                                                                                                                                             |

| bisledd rt, ra    | Branch indirect and set link on external data, disable. The address of the instruction following this instruction is placed in word element 0 of register $rt$ , and all other elements of register $rt$ are assigned a value of zero. If the count of channel 0 is nonzero, the branch is taken, and execution continues at the effective address in word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. If the count of channel 0 is zero, execution continues with the next sequential instruction. If the branch is taken, interrupts are disabled; otherwise, the interrupt enable state remains unchanged. |

| bislede rt, ra    | Branch indirect and set link on external data, enable. The address of the instruction following this instruction is placed in word element 0 of register $rt$ , and all other elements of register $rt$ are assigned a value of zero. If the count of channel 0 is nonzero, the branch is taken, and execution continues at the effective address in word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. If the count of channel 0 is zero, execution continues with the next sequential instruction. If the branch is taken, interrupts are enabled; otherwise, the interrupt enable state remains unchanged.   |

| biz rc, ra        | Branch indirect if zero word. If word element 0 of register $rc$ is zero, execution proceeds at the effective address in word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. If word element 0 of $rc$ is nonzero, execution proceeds with the next sequential instruction.                                                                                                                                                                                                                                                                                                                                      |

| bizd rc, ra       | Branch indirect if zero word, disable. If word element 0 of register $rc$ is zero, the branch is taken, and execution proceeds at the effective address in word element 0 of register $ra$ . The 2 least significant bits of this address are ignored. If word element 0 of $rc$ is nonzero, execution proceeds with the next sequential instruction. If the branch is taken, interrupts are disabled; otherwise, the interrupt enable state remains unchanged.                                                                                                                                                                                          |

| bize rc, ra       | Branch indirect if zero word, enable. If word element 0 of register $rc$ is zero,<br>the branch is taken, and execution proceeds at the effective address in word<br>element 0 of register $ra$ . The 2 least significant bits of this address are<br>ignored. If word element 0 of $rc$ is nonzero, execution proceeds with the next<br>sequential instruction. If the branch is taken, interrupts are enabled; otherwise,<br>the interrupt enable state remains unchanged.                                                                                                                                                                             |

7

| Instruction/Usage | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| br s18            | Branch relative. Execution proceeds with the instruction addressed by the sum of the current instruction address and the sign-extended value of $s18$ . The 2 least significant bits of $s18$ are ignored.                                                                                                                                                                                     |

| bra s18           | Branch absolute. Execution proceeds with the instruction addressed by the sign-extended value of $s18$ . The 2 least significant bits of $s18$ are ignored.                                                                                                                                                                                                                                    |

| brasl rt, s18     | Branch absolute and set link. Execution proceeds with the instruction<br>addressed by the sign-extended value of $s18$ . The 2 least significant bits of<br>s18 are ignored. The instruction following the current instruction is placed in<br>word element 0 of register rt, and all other elements of rt are assigned a<br>value of zero.                                                    |

| brhnz rc, s18     | Branch if not zero halfword. If the halfword element 1 of register $rc$ is nonzero, execution proceeds with the instruction addressed by the sum of the current instruction address and the sign-extended value of s18. The 2 least significant bits of s18 are ignored. If halfword element 1 of $rc$ is zero, execution proceeds with the next sequential instruction.                       |

| brhz rc, s18      | Branch if zero halfword. If the halfword element 1 of register $rc$ is zero,<br>execution proceeds with the instruction addressed by the sum of the current<br>instruction address and the sign-extended value of s18. The 2 least significant<br>bits of s18 are ignored. If the halfword element 1 of register $rc$ is nonzero,<br>execution proceeds with the next sequential instruction.  |

| brnz rc, s18      | Branch if not zero word. If the word element 0 of register $rc$ is nonzero,<br>execution proceeds with the instruction addressed by the sum of the current<br>instruction address and the sign-extended value of s18. The 2 least significant<br>bits of s18 are ignored. If word element 0 of register $rc$ is zero, execution<br>proceeds with the next sequential instruction.              |

| brsl rt, s18      | Branch relative and set link. Execution proceeds with the instruction addressed<br>by the sum of the current instruction address and the sign-extended value of<br>s18. The 2 least significant bits of $s18$ are ignored. The instruction following<br>the current instruction is placed in word element 0 of register $rt$ , and all other<br>elements of $rt$ are assigned a value of zero. |

| brz rc, s18       | Branch if zero word. If the word element 0 of register $rc$ is zero, execution<br>proceeds with the instruction addressed by the sum of the current instruction<br>address and the sign-extended value of s18. The 2 least significant bit of s18<br>are ignored. If word element 0 of register $rc$ is nonzero, execution proceeds<br>with the following instruction.                         |

| cbd rt, u7(ra)    | Generate controls for byte insertion (d-form). A control mask is generated that can be used by the shufb instruction to insert a byte at the effective address computed by the sum of register ra and the unsigned value u7. The control mask is placed in register rt.                                                                                                                        |

| cbx rt, ra, rb    | Generate controls for byte insertion (x-form). A control mask is generated that can be used by the shufb instruction to insert a byte at the effective address computed by the sum of registers ra and rb. The control mask is placed in register rt.                                                                                                                                          |

| cdd rt, u7(ra)    | Generate controls for doubleword insertion (d-form). A control mask is generated that can be used by the shufb instruction to insert a doubleword at the effective address computed by the sum of register ra and unsigned value u7. The control mask is placed in register rt.                                                                                                                |

| cdx rt, ra, rb    | Generate controls for doubleword insertion (x-form). A control mask is generated that can be used by the shufb instruction to insert a doubleword at the effective address computed by the sum of registers ra and rb. The control mask is placed in register rt.                                                                                                                              |

| Instruction/Usage    | Description                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ceq rt, ra, rb       | Compare equal word. Each word element of register $ra$ is compared with the corresponding word element of register $rb$ . If the two elements are equal, all ones are placed in the corresponding word element of register $rt$ . Otherwise, the two elements are not equal, and zero is placed in the corresponding word element of register $rt$ .                                                                                     |

| ceqb rt, ra, rb      | Compare equal byte. Each byte element of register ra is compared with the corresponding byte element of register rb. If the two elements are equal, all ones are placed in the corresponding byte element of register rt. Otherwise, the elements are not equal, and zero is placed in the corresponding byte element of register rt.                                                                                                    |

| ceqbi rt, ra, s10    | Compare equal byte immediate. Each byte element of register $ra$ is compared with the 8 least significant bits of s10. If the two values are equal, all ones are placed in the corresponding byte element of register rt. Otherwise, the values are not equal, and zero is placed in the corresponding byte element of register rt.                                                                                                      |

| ceqh rt, ra, rb      | Compare equal halfword. Each halfword element of register ra is compared<br>with the corresponding halfword element of register rb. If the two elements are<br>equal, all ones are placed in the corresponding halfword element of register<br>rt. Otherwise, the elements are not equal, and zero is placed in the<br>corresponding halfword element of register rt.                                                                    |

| ceqhi rt, ra, s10    | Compare equal halfword immediate. Each halfword element of register ra is compared with the 16-bit sign-extended value s10. If the two values are equal, all ones are placed in the corresponding halfword element of register rt. Otherwise, the values are not equal, and zero is placed in the corresponding halfword element of register rt.                                                                                         |

| ceqi rt, ra, s10     | Compare equal word immediate. Each word element of register ra is<br>compared with the 32-bit sign-extended value s10. If the two values are equal,<br>all ones are placed in the corresponding word element of register rt.<br>Otherwise, the values are not equal, and zero is placed in the corresponding<br>word element of register rt.                                                                                             |

| cflts rt, ra, scale7 | Convert floating to signed integer. Each floating-point element of register ra is multiplied by $2^{\text{scale7}}$ , converted to a signed 32-bit integer, and placed in the corresponding word element of register rt. Values outside of the range from $-2^{31}$ to $2^{31}$ -1 are clamped (saturated to the nearest bound).                                                                                                         |

| cfltu rt, ra, scale7 | Convert floating to unsigned integer. Each floating-point element of register $ra$ is multiplied by $2^{scale7}$ , converted to an unsigned 32-bit integer, and placed in the corresponding word elements of register $rt$ . Values outside of the range from 0 to $2^{32}$ -1 are clamped (saturated to the nearest bound).                                                                                                             |

| cg rt, ra, rb        | Carry generate word. Each word element of register $ra$ is added to the corresponding word element of register $rb$ . The carry out is placed in the least significant bit of the corresponding word element of register $rt$ , and 0 is placed in the remaining bits of $rt$ .                                                                                                                                                          |

| cgt rt, ra, rb       | Compare greater than word. Each word element of register ra is compared<br>with the corresponding word element of register rb. If the word in ra is greater<br>than the corresponding word in rb, all ones are placed in the corresponding<br>word element of register rt. Otherwise, the word in ra is less than or equal to<br>the corresponding word in rb, and zeros are placed in the corresponding word<br>element of register rt. |

| Instruction/Usage | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cgtb rt, ra, rb   | Compare greater than byte. Each byte element of register ra is compared with the corresponding byte element of register rb. If the byte in ra is greater than the corresponding byte in rb, all ones are placed in the corresponding byte element of register rt. Otherwise, the byte in ra is less than or equal to the corresponding byte in rb, and zeros are placed in the corresponding byte element of register rt.                                                    |

| cgtbi rt, ra, s10 | Compare greater than byte immediate. Each byte element of register ra is<br>compared with the 8 least significant bits of $s10$ . If the byte in ra is greater<br>than the corresponding byte in $s10$ , all ones are placed in the corresponding<br>byte element of register rt. Otherwise, the byte in ra is less than or equal to<br>the corresponding byte in $s10$ , and zeros are placed in the corresponding byte<br>element of register rt.                          |

| cgth rt, ra, rb   | Compare greater than halfword. Each halfword element of register ra is<br>compared with the corresponding halfword element of register rb. If the<br>halfword in ra is greater than the corresponding halfword in rb, all ones are<br>placed in the corresponding halfword element of register rt. Otherwise, the<br>halfword in ra is less than or equal to the corresponding halfword in rb, and<br>zeros are placed in the corresponding halfword element of register rt. |

| cgthi rt, ra, s10 | Compare greater than halfword immediate. Each halfword element of register ra is compared with the 16-bit sign-extended value $s10$ . If the halfword in ra is greater than $s10$ , all ones are placed in the corresponding halfword element of register rt. Otherwise, the halfword in ra is less than or equal to $s10$ , and zeros are placed in the corresponding halfword element of register rt.                                                                      |

| cgti rt, ra, s10  | Compare greater than word immediate. Each word element of register ra is compared with the 32-bit sign-extended value s10. If the word in ra is greater than s10, all ones are placed in the corresponding word element of register rt. Otherwise, the word in ra is less than or equal to s10, and zeros are placed in the corresponding word element of register rt.                                                                                                       |

| cgx rt, ra, rb    | Carry generate word extended. For each word element in registers ra and rb,<br>a carry out is generated by summing the element of register ra, the<br>corresponding element of rb, and the least significant bit of rt. The carry out<br>is placed in the least significant bit of the corresponding word element of rt,<br>and zeros are placed in the remaining bits.                                                                                                      |

| chd rt, u7(ra)    | Generate controls for halfword insertion (d-form). A control mask is generated that can be used by the shufb instruction to insert a halfword at the effective address computed by the sum of register ra and the unsigned value u7. The control mask is placed in register rt.                                                                                                                                                                                              |

| chx rt, ra, rb    | Generate controls for halfword insertion (x-form). A control mask is generated that can be used by the shufb instruction to insert a halfword at the effective address computed by the sum of registers $ra$ and $rb$ . The control mask is placed in register $rt$ .                                                                                                                                                                                                        |

| clgt rt, ra, rb   | Compare logical greater than word. Each word element of register ra is<br>logically compared with the corresponding word element of register rb. If the<br>word in ra is greater than the corresponding word in rb, all ones are placed in<br>the corresponding word element of register rt. Otherwise, the word in ra is<br>less than or equal to the corresponding word in rb, and zeros are placed in<br>the corresponding word element of register rt.                   |

| Instruction/Usage    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clgtb rt, ra, rb     | Compare logical greater than byte. Each byte element of register ra is<br>logically compared with the corresponding byte element of register rb. If the<br>byte in ra is greater than the corresponding byte in rb, all ones are placed in<br>the corresponding byte element of register rt. Otherwise, the byte in ra is<br>less than or equal to the corresponding byte in rb, and zeros are placed in the<br>corresponding byte element of register rt.                      |

| clgtbi rt, ra, s10   | Compare logical greater than byte immediate. Each byte element of register ra is logically compared with the 8 least significant bits of $s10$ . If the byte in ra is greater than the value in $s10$ , all ones are placed in the corresponding byte element of register rt. Otherwise, the byte in ra is less than or equal to the byte in $s10$ , and zeros are placed in the corresponding byte element of register rt.                                                     |

| clgth rt, ra, rb     | Compare logical greater than halfword. Each halfword element of register ra is logically compared with the corresponding halfword element of register rb. If the halfword in ra is greater than the corresponding halfword in rb, all ones are placed in the corresponding halfword element of register rt. Otherwise, the halfword in ra is less than or equal to the corresponding halfword in rb, and zeros are placed in the corresponding halfword element of register rt. |

| clgthi rt, ra, s10   | Compare logical greater than halfword immediate. Each halfword element of register ra is logically compared with the 16-bit sign-extended value $s10$ . If the halfword in ra is greater than the value in $s10$ , all ones are placed in the corresponding halfword element of register rt. Otherwise, the halfword in ra is less than or equal to the value in $s10$ , and zeros are placed in the corresponding halfword element of register rt.                             |

| clgti rt, ra, s10    | Compare logical greater than word immediate. Each word element of register ra is logically compared with the 32-bit sign-extended value $s10$ . If the word in ra is greater than the value in $s10$ , all ones are placed in the corresponding word element of register rt. Otherwise, the word element in ra is less than or equal to the value in $s10$ , and zeros are placed in the corresponding word element of register rt.                                             |

| clz rt, ra           | Count leading zeros. The number of zeros to the left of the first 1 in each word element of register $ra$ is counted, and the resulting count is placed in the corresponding element of register $rt$ .                                                                                                                                                                                                                                                                         |

| cntb rt, ra          | Count ones in bytes. The number of ones in each byte element of register ra is counted, and the resulting count is placed in the corresponding element of register rt.                                                                                                                                                                                                                                                                                                          |

| csflt rt, ra, scale7 | Convert signed integer to floating. Each signed word element of register ra is converted to floating-point, multiplied by 2 <sup>-scale7</sup> , and placed in the corresponding floating-point elements of register rt.                                                                                                                                                                                                                                                        |

| cuflt rt, ra, scale7 | Convert unsigned integer to floating. Each unsigned word element of register ra is converted to floating-point, multiplied by $2^{-scale7}$ , and placed in the corresponding floating point elements of register rt.                                                                                                                                                                                                                                                           |

| cwd rt, u7(ra)       | Generate controls for word insertion (d-form). A control mask is generated that can be used by the shufb instruction to insert a word at the effective address computed by the sum of register ra and the unsigned value u7. The control mask is placed in register rt.                                                                                                                                                                                                         |

| cwx rt, ra, rb       | Generate controls for word insertion (x-form). A control mask is generated that can be used by the shufb instruction to insert a word at the effective address computed by the sum of registers ra and rb. The control mask is placed in register rt.                                                                                                                                                                                                                           |

Instruction/Usage

dfa rt, ra, rb

dfceq rt, ra, rb

dfcgt rt, ra, rb

dfcmeq rt, ra, rb

| _ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | Double floating add. Each double floating-point element of register ra is added to the corresponding double floating-point element of register rb, and the results are placed in the corresponding elements of register rt.                                                                                                                                                                                                                                                                              |

|   | Double floating compare equal. Each double floating-point element of register ra is compared with the corresponding double floating-point element of register rb. If the two elements are equal, all ones are placed in the corresponding double-word element of register rt. Otherwise, if they are not equal, zeros are placed in the corresponding double-word element of register rt.                                                                                                                |

|   | Double floating compare greater than. Each double floating-point element of register ra is compared with the corresponding double floating-point element of register rb. If the element in ra is greater than the corresponding element of register rb, all ones are placed in the corresponding double-word element of register rt. Otherwise, if the element in ra is less than or equal to the corresponding element in rb, zeros are placed in the corresponding double-word element of register rt. |

|   | Double floating compare magnitude equal. The absolute value of each double floating-point element of register ra is compared with the absolute value of the corresponding double floating-point element of register rb. If the two elements are equal, all ones are placed in the corresponding double-word element of register rt. Otherwise, if they are not equal, zeros are placed in the corresponding double-word element of register rt.                                                          |

|   | Double floating compare magnitude greater than. The absolute value of each double floating-point element of register ra is compared with the absolute value of the corresponding double floating-point element of register rb. If the                                                                                                                                                                                                                                                                    |

|                   | are equal, all ones are placed in the corresponding double-word element of register rt. Otherwise, if they are not equal, zeros are placed in the corresponding double-word element of register rt.                                                                                                                                                                                                                                                                                           |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dfcmgt rt, ra, rb | Double floating compare magnitude greater than. The absolute value of each double floating-point element of register ra is compared with the absolute value of the corresponding double floating-point element of register rb. If the element in ra is greater than the corresponding element of register rb, all ones are placed in the corresponding double-word element of register rt. Otherwise, if the element in ra is less than or equal to the corresponding element of register rt. |

| dfm rt, ra, rb    | Double floating multiply. Each double floating-point element of register ra is multiplied by the corresponding double floating-point element of register rb, and the results are placed in the corresponding elements of register rt.                                                                                                                                                                                                                                                         |

| dfma rt, ra, rb   | Double floating multiply and add. Each double floating-point element of register ra is multiplied by the corresponding double floating-point element of register rb, and the corresponding double floating-point element of register rt is then added to the product. The results are placed in the corresponding elements of register rt.                                                                                                                                                    |

| dfms rt, ra, rb   | Double floating multiply and subtract. Each double floating-point element of register $ra$ is multiplied by the corresponding double floating-point element of register $rb$ , and the corresponding double floating-point element of register $rt$ is subtracted from the product. The results are placed in the corresponding elements of register $rt$ .                                                                                                                                   |

| dfnma rt, ra, rb  | Double floating negative multiply and add. Each double floating-point element<br>of register $ra$ is multiplied by the corresponding double floating-point element<br>of register $rb$ , and the corresponding double floating-point element of register<br>rt is added to the product. Each result is negated and placed in the<br>corresponding element of register $rt$ .                                                                                                                  |

| dfnms rt, ra, rb  | Double floating negative multiply and subtract. Each double floating-point<br>element of register ra is multiplied by the corresponding double floating-point<br>element of register rb, and the product is subtracted from the corresponding<br>double floating-point element of register rt. The results are placed in<br>corresponding elements of register rt.                                                                                                                            |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Instruction/Usage | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dfs rt, ra, rb    | Double floating subtract. Each double floating-point element of register rb is subtracted from the corresponding double floating-point element of register ra, and the results are placed in the corresponding elements of register rt.                                                                                                                                                                                                                                                                                          |

| dftsv rt, ra, u7  | Double floating test special value. Each double floating-point element of register ra is tested for the special values as specified by the immediate value u7. If one of the specified tests is true, all ones are placed in the corresponding double-word element of register rt. Otherwise, if none of the tests are true, zeros are placed in the corresponding double-word element of register rt.                                                                                                                           |

| dsync             | Synchronize data. All pending store operations to local storage memory are completed before the processor proceeds to the next instruction.                                                                                                                                                                                                                                                                                                                                                                                      |

| eqv rt, ra, rb    | Equivalent. The value in register ra is logically exclusive ORed with the value in register rb, and the complement of the result is placed in register rt.                                                                                                                                                                                                                                                                                                                                                                       |